为满足深亚微米(DSM)系统级芯片(SoC)设计的性能和可靠性要求,设计良好的电源分配网络十分重要。随着器件密度和时钟频率的增加,电源线和地线网络传送的交换电流也同样增加,进而导致功率密度的增加,由于在DSM设计中采用的低电源电压以及更细的线路,功率密度的增加将对电源网络(Power Grid)的鲁棒性产生不利影响。由于瞬间的高电流和电源线路的阻抗引起的器件电压的大幅度下降,电源网络更易受电压降的影响,这就是通常所说的IR压降现象。

由于大量持续不变的电流引起的电迁移效应,电源线路更容易失效,也易与附近的线路形成短路。IR压降不仅影响电源网络的完整性,而且延长了时序收敛的时间。门电路的供电电压降低百分之五可以使门电路的延迟增加百分之十五。这些DSM效应使得电源网络验证已成为一个必不可少的设计过程,以确保新设计达到目标设计速度、满足可靠性要求并且具备可制造性。

电源设计面临的关键问题

电源网络验证的一个关键问题在于,到目前为止,都是在版图设计完成之后才在设计流程中利用商用电源网络验证工具进行电源网络设计。在设计后期,电源线路的互连寄生参数以及器件的电流消耗的大部分详细数据已经完成,因而如果此时校正经验证过的任何一处电源网络问题,大量返工的代价非常昂贵。

TI公司已经为综合了门级和晶体管级分析的SoC设计开发了一种新的分层式电源网络验证方法。该多级分层式验证方法能够提取电流在SoC芯片中的流动和分布情况,以便在物理设计周期或早在底层规划阶段发现潜在的电源网络问题。例如TI的TMS320C6211 DSP芯片设计就是采用了这种新方法。

要利用新的电源网络验证方法,首先必须定义设计要求。SoC在单个芯片上集成了多级逻辑和功能,也就是说,单片电路上集成了扁平(Flat)门级综合逻辑、分层门级模块(如数据路径)、晶体管级嵌入式IP模块(如微处理器内核或存储器)以及模拟电路等,因此,SoC验证方法必须具备分层式的结构,并包括门级和晶体管级验证。

在设计早期进行门级分析,有利于设计顶层电源网络,并有利于针对未安置模块规定电源网络要求。

然而,仅依靠门级分析对电源网络验证PGS(Power Grid sign-off)来说不够精确,因此,该方法必须包括电源网络验证,它在晶体管级对单元或者IP模块的内部电源网络进行建模,以便获得精确的电流分配情况。

设计复用是SoC设计的核心,新方法要易于实现单元、模块以及IP的复用。当一个单元或者IP模块分析完成后,分析结果必须具备可复用性,因而避免为每个实例重新提取和重新分析该单元或IP模块,分析结果的可复用性将对整个芯片电源网络验证的周期影响很大。我们选择Simplex Solutions公司的Voltage Storm(VS)SoC设计工具,该工具能满足TI对多级和分层式方法的所有要求。

电源网络验证新方法

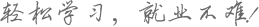

TI采用Simplex工具进行开发的方法如图1所示。首先,库设计小组对包括IP内核、存储器和标准单元在内的所有叶片级(leaf-level)组件进行特征参数提取和验证。这些电源网络特征参数由GDSII版图文件在晶体管级生成,以便精确地对电流分配建模。根据这些特征参数,库设计人员能够创建在验证过程中使用的各种电源网络视图,包括底层规划(或者模板)视图、端口(或黑盒)视图以及详细的(或晶体管级)视图。

底层规划视图由以下一些信息得出,包括:单元或者模块端口的LEF描述;单元的高度、宽度、间距信息;用于电源布线的每个金属层的方位等。

端口视图是一个不带晶体管的黑盒视图,由某个单元库的LEF描述来创建。它在该模块的外围端口还配有电流源,把电流均匀地分配到各端口。这个模型用于对底层规划阶段的标准单元建模,但不足以应付更复杂的IP模块和PGS的应用设计要求。

IP模块和标准单元的详细电源网络视图由端口的LEF描述和版图的GDSII描述来创建。详细的视图组件包括来自LEF的端口几何形状、来自GDSII的内部电源网络以及来源于GDSII版图的晶体管抽头点的电流源。具体视图包含晶体管级的详细信息,可精确地模拟复杂IP模块内部的电流分配和功耗情况。

在设计流程的下一步,芯片集成或物理设计小组利用布线的DEF描述及由库设计小组创建的电源网络视图库对底层规划进行分析,模块设计人员可以使用类似的方法分析他们设计的模块。

如果DEF与用于输出的GDSII版图文件一致,那么对于大多数ASIC流程而言,一旦所有单元和IP模块已经跟电源布线放置在一起,则进行的PGS。在这个设计阶段,根据已经确定的电源网络的完整性数据,设计人员可避免为电源网络留出过多的空间,并使信号布线面积。

验证新的设计方法

如果在布局布线之后,设计小组又对的设计进行了重要的修改,那么物理验证小组负责进行版图与原理图验证,并检查设计规则,同时在晶体管级执行PGS以及在的GDSII版图上进行一次扁平分析(flat analysis)。

用于验证新方法的芯片是TMS320C6211,是带有一个两级高速缓存结构的定点VLIW数字信号处理器。C6211采用五层金属工艺,包含600万个晶体管,在这个DEF中有大约1.16万个布线网络,放置了2.29万个对象,标称工作电压是1.8V。

步:生成电源网络视图。

首先,要创建TMS320C6211各种组件的电源网络视图库。C6211包含一个C62xVLIW DSP内核和17个嵌入式SRAM。在DSP内核和嵌入式SRAM中,由于电流分布的非均匀,很有必要利用VS SoC工具创建的详细电源网络视图的晶体管级建模。TI的开发人员也创建了若干组件的底层规划视图,以便在底层规划过程中使用。

第二步:在底层规划过程中进行分析。

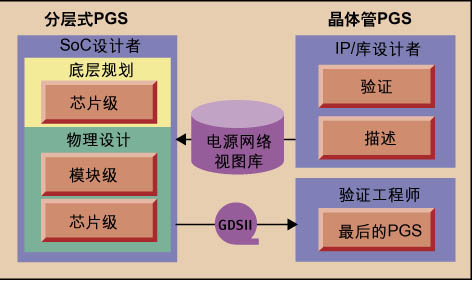

在底层规划过程的早期,模块的其余部分还未创建,所以能够修改DSP内核的版图。用于全芯片分析的VS SoC输入包括:全局电源布线的芯片级DEF、基于实例的功耗数据、DSP内核的详细晶体管级视图以及其它模块的底层规划视图(图2)。该分析的执行发生在全局电源布线和布局之后、信号线布线之前,使人们能看到通过DSP内核的电流及其对附近逻辑电路的影响。在400MHz的SUN Ultrasparc-II工作站上,该分析仅需要运行六分钟并占用60MB存储器。

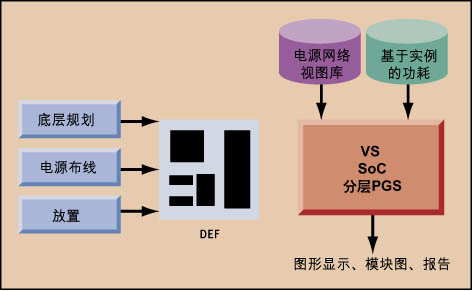

分析表明,电源布线太保守,其实增加IR压降的容限仍然可以达到设计要求。在VS SoC中使用PGS探测特性来检查改变电源布线的DEF的影响。利用“Scaling”特性,可以在高IR压降区域增加走线和过孔,在低IR压降区域删除走线和过孔。电压从1.774V下降到1.770V,仍在规定范围之内,从而节省了宝贵的布线资源。

第三步:电源网络验证

在完成全局电源布线、单元放置和信号线布线之后,接着就进行全芯片分层式电源网络IR压降验证。用于该分析的VS SoC输入包括信号和电源布线的芯片级DEF、基于实例的功耗以及DSP内核、SRAM和标准单元的详细视图。

为了对每个模块进行精确的功耗估计,TI使用Synopsys公司的晶体管级仿真工具Powermill。对于版图设计前分析,要创建Powermil所需的SPICE模型架构(deck),该SPICE模型架构则通过Synopsys包含对线电容的线负载模型估值的已综合数据库得到。对于版图设计后分析,开发人员根据版图设计后EDIF网表创建Powermill所需的SPICE模型架构,该EDIF网表包含用Simplex的Fire&Ice QX提取的后端注释寄生电容。

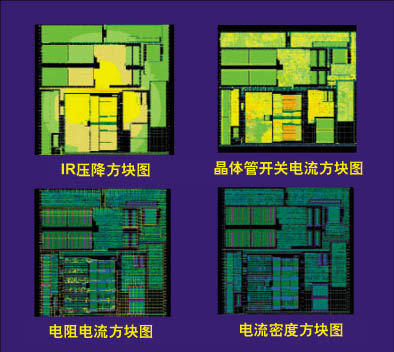

在定型的DEF上用VS SoC进行全芯片分层式分析, 400MHz的SUN Ultrasparc-II工作站需要运行22分钟并占用550MB存储器。除了IR压降分析,全芯片分析还产生了其他一些电源网络信息,包括电阻电流、抽头电流(tap current)和电流密度方块图。图4的方块图将电源网络的行为形象地表现出来,例如,抽头电流的分配表明存储器中电流非常低,DSP内核中的电流较高,正如预期那样。

验证精度

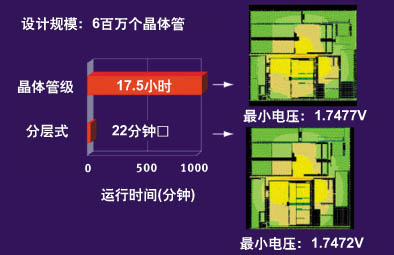

利用VS SoC的DEF分析速度很快,与现有的版图设计后晶体管级电源网络提取和分析所用的17.5个CPU小时相比,它只需要22个CPU分钟,但是,分析精度也很重要。为了验证分层式分析的精度,开发人员利用现有的电源网络验证方法,在定型的GDSII版图上对该电源网络进行了一项扁平的、晶体管级的分析。

根据该分析计算出的小工作电压为1.7477V,IR压降为0.0523V;而根据分层式分析计算出的小工作电压为1.7472V,IR压降为0.0528V,几乎与晶体管级分析的结果相同,误差在0.1%以内。

Simplex将精度的提高归因于Accura静态分析专有技术,它能分析时钟域、识别存储器和门电路,并根据基本输入分析传输行为。

对时序的影响

非均匀电源分配会影响芯片性能,因此必须对其进行DSM SoC时序验证。在讨论时序收敛环路时,IR压降对时序的影响已被忽略,这是因为很难获得IR压降对时序影响的数据,也很难获得扁平晶体管级分析的长期循环时间数据。试验表明,将VS SoC分层式分析得到的基于实例的IR压降数据加入到延迟计算器(Synopsys的Primetime),可以获得IR压降对时序的影响。

开发人员用手工方法将基于实例的IR压降数据加入Primetime工具,并建立了用于不同级别的IR压降(2%、5%、10%)的多个Synopsys单元库,然后,根据VS SoC得到的IR压降数据为Primetime分析选择库单元。

本文结论

电源网络验证SoC设计方法的一个重要组成部分。利用VS SOC能够开发一种新型用于包含门级和晶体管级分析的电源网络验证的分层式方法。TI的开发人员现在能够使其设计中的电流表现可视化,并且在物理设计早期验证其电源网络设计的完整性。早期分析使设计者容易实现对电源网络的修改且成本。

电源网络验证也避免了不必要且普遍存在的电源网络设计冗余度太大的问题,并且还能显示时序验证流程中的IR压降等数据。